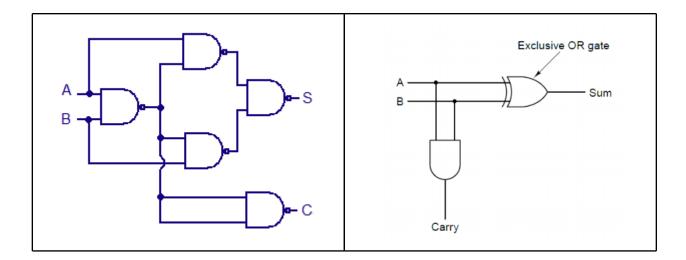

## Half Adder

NOTE11: The various forms of a half adder

## Text reference: **Section 3.2**

Binary addition - 4 cases for adding two bits:

| A<br>+ B | 0<br>+ 0 | 0<br>+ 1 | 1<br>+ 0 | 1<br>+ 1          |

|----------|----------|----------|----------|-------------------|

| SUM      | 0        | <br>1    |          | 0                 |

|          |          |          |          | ~> carry<br>the 1 |

This is called a **half adder**.

- 2 inputs are A, B

- 2 outputs are SUM and CARRY

There is (always) 1 truth table.

| Α | В | SUM | CARRY |

|---|---|-----|-------|

| 0 | 0 | 0   | 0     |

| 0 | 1 | 1   | 0     |

| 1 | 0 | 1   | 0     |

| 1 | 1 | 0   | 1     |

There are many possible equivalent **Boolean equations**.

| // using nand gates    |  |

|------------------------|--|

| SUM = [(AB')' (A'B)']' |  |

| CARRY = (AB')'         |  |

|                        |  |

There are many equivalent logic gate implementations.

There are many equivalent Verilog HDL descriptions.

```

// half_adder.v

// gate-level Half Adder

//

module half_adder( A, B, SUM, CARRY);

input A;

input B;

output SUM;

output CARRY;

xor u1( SUM, A, B);

and u2( CARRY, A, B);

endmodule

```